| File Type | Extension | Icon | Description | New Source Wizard Behavior/Tool Launched |

|---|---|---|---|---|

| Block RAM Memory Map (BMM File) | .bmm | Used in PowerPC® and MicroBlaze™ processor designs to describe the organization of Block RAM memory. | Opens the file in the text editor you specify in the Editors page of the Preferences dialog box. The CPU executable code is automatically inserted in the configuration file during design implementation. | |

| ChipScope Definition and Connection (CDC File) | .cdc | Contains generic information about the trigger and data ports of the ChipScope™ core. | Adds the file to the project. Double-click the CDC file in the Hierarchy pane of the Design panel to run the implementation process and launch the ChipScope Pro Core Inserter. For details, see the ChipScope Pro Tool Debugging Overview. Note The ChipScope Pro tool must be installed for this source type to be available. | |

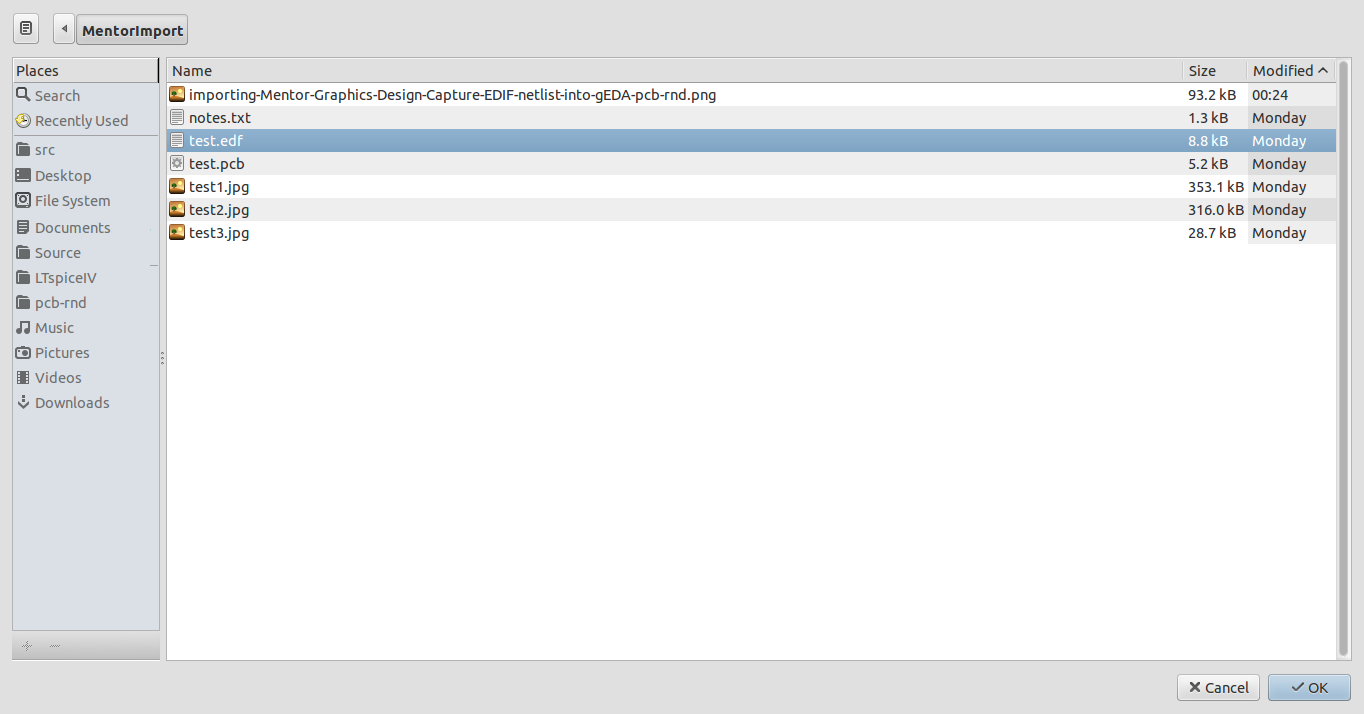

| Electronic Data Interchange Format (EDIF) | .edn, .edf, .edif, .sedif | Specifies the design netlist in an industry standard file format. | Must be generated by a third-party design entry tool and added to the project. Note You can only add an EDIF file as a top-level module, not as a lower-level module. If you are using hierarchical EDIF files, lower-level EDIF files are automatically processed during the implementation process. | |

| ELF | .elf | Note Only one ELF file is allowed per project. | Must be generated by the Data2MEM command line tool and added to the project. | |

| Embedded Processor | .xmp | Embedded microprocessor project file created with Xilinx Platform Studio. | Launches the Xilinx Platform Studio in which you can define the embedded processor system portion of your design. For details, see the Embedded Development Kit Documentation. | |

| Implementation Constraints File | .ucf | Contains user-specified logical constraints. | Adds the file to the project. Double-click the UCF file in the Hierarchy pane of the Design panel, or double-click a Constraints Entry process in the Processes pane to open the file. You can assign multiple UCFs to the top-level module. For details, see Constraints Entry Methods. | |

| IP (Architecture Wizard) | .xaw | Contains predefined logic functions that configure architecture features or modules. | Launches one of the Xilinx Architecture Wizards in which you can define your IP. For details, see Working with Architecture Wizard IP. | |

| IP (CORE Generator) | .xco | Contains predefined logic functions. | Launches one of the Xilinx IP core customization tools in which you can define your IP. For details, see Working with CORE Generator™ IP. | |

| Memory Definition (MEM File) | .mem | Used to define the contents of memory (RAMB4 and RAMB16). | Opens the file in the text editor you specify in the Editors page of the Preferences dialog box. The CPU executable code is automatically inserted in the configuration file during design implementation. | |

| Schematic | .sch | Contains a schematic design. | Opens the schematic file in the Project Navigator Workspace. For details, see the Schematic Overview. | |

| System Generator module | .sgp | Contains Digital Signal Processing (DSP) system module created with System Generator for DSP. | N/A | |

| Targeted device, package, and speed grade | N/A | Shows the targeted device, package, and speed grade. | N/A | |

| Undefined | N/A | Contains an instantiated module that has not been added to the ISE project but is referenced by a source file in the ISE project. | N/A | |

| User Document | Multiple file types | Contains user information that is not implemented with the project, for example, supporting documentation. | N/A | |

| Verilog Module | .v | Contains Verilog design code. | Opens the file in the text editor you specify in the Editors page of the Preferences dialog box. | |

| Verilog Test Fixture | .v | Defines the stimulus to the ports of an HDL file. | Prompts you to associate the file with a Verilog source module and then opens a skeleton test bench file in the text editor you specify in the Editors page of the Preferences dialog box. | |

| VHDL Library | N/A | Contains a collection of VHDL packages. | Adds a new directory to the vhdl library directory in the Libraries panel. | |

| VHDL Module | .vhd | Contains VHDL design code. | Opens the file in the text editor you specify in the Editors page of the Preferences dialog box. | |

| VHDL Package | .vhd | Contains definitions, macros, sub-routines, supplemental types, subtypes, constants, functions, and other files. | Opens the file in the text editor you specify in the Editors page of the Preferences dialog box. | |

| VHDL Test Bench | .vhd | Defines the stimulus to the ports of an HDL file. | Prompts you to associate the file with a VHDL source and then opens a skeleton test bench file in the text editor you specify in the Editors page of the Preferences dialog box. |

- Netlist Basics. The load feature is loaced in the setup tab of the netlist tool and in the Utilities menu. Supported formats are: spice, structual VHDL, alliance, qucs, eagle, PADSpcb and OpenAccess. Support for other file format can be extended on request. Most netlist formats refer to its devices by a name.

- Netlist File Format. Netlists can be imported into the ExpressPCB layout program using the format described in this document. The netlist file is an ASCII text file. The filename should include the '.net.

File Format Excel

Answer: Files which are given the.EDN extension are known as EDIF Netlist files, however other file types may also use this extension. If you are aware of any additional file formats that use the EDN extension, please let us know. File Type 1EDIF Implementation Netlist File. File format categories include Binary, Text, XML, and Zip. The format of this file type has not been determined. EDIF import and conversion are two drastically different things. Import refers to the importing of the file and Gate-way’s automatic library and cell generation of what the EDIF file contains. Conversion is the process of turning this imported data into a useful netlist that is able to sim-ulate and represent the circuit as faithfully as.